# International Journal of Recent Innovations in Academic Research

This work is licensed under a Creative Commons Attribution 4.0 International License [CC BY 4.0]

E-ISSN: 2635-3040; P-ISSN: 2659-1561 Homepage: https://www.ijriar.com/ Volume-9, Issue-3, July-September-2025: 203-206

#### **Research Article**

# Innovative Chips Design: Partial Thin Wall Layer Approach (PTWL)

### **Lie Chun Pong**

MEd, CUHK (Chinese University of Hong Kong), MSc, HKUST (Hong Kong University of Science and Technology)

Email: vincentcplie@vahoo.com.hk

**Received:** July 29, 2025 Accepted: August 17, 2025 Published: August 23, 2025

#### **Abstract**

Integrated circuits (ICs) and chips are important for technological progress and economic growth in the semiconductor sector. It involves complex tech issues like process limits, quantum effects at the nanoscale, and material constraints such as dielectric breakdown and electron mobility to boost industry resilience through collaborations focused on improving power efficiency, heat management, and advanced interconnect techniques. In this research paper, we aim to introduce an innovative concept approach, the partial thin wall layer (PTWL) approach, to enhance the efficiency and applicability of memory chips.

Keywords: Integrated Circuits (ICs), Chips, Partial Thin Wall Layer, PTWL Approach.

#### Introduction

Chips, also known as integrated circuits (ICs), are fundamental components driving technological innovation and economic development within the semiconductor sector [1]. The strategic significance encompasses attracting significant, addressing complex technological challenges such as process scaling limits governed by Moore's Law, quantum effects emerging at nanoscale dimensions, and fundamental material constraints related to dielectric breakdown and electron mobility. Moreover, they contribute to enhancing industry resilience through collaborative efforts targeting power efficiency optimization, thermal management, and advanced interconnect routing paradigms [1, 2].

Key focus areas include semiconductor physics-covering carrier transport, band structure engineering, and defect mechanics as well as nanofabrication techniques such as atomic layer deposition, reactive ion etching, and epitaxial growth. Advanced packaging methodologies like 2.5D/3D integration and heterogeneous integration are crucial for performance improvements.

As information and communication technologies (ICT) evolve, particularly with the integration of computer devices [2] and data memory these advancements facilitate the development of highly automated, cyber-physical systems, and intelligent manufacturing processes. These practices are instrumental in transforming production methodologies by enabling real-time flash memory and scalable data-driven memory-making [1, 2].

#### Discussion

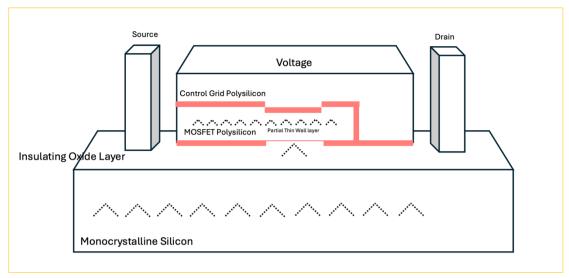

Traditional barrier of using the method of bipolar junction transistors (BJTs) and field-effect transistors (FETs) are fundamental semiconductor devices characterized by structures that facilitate the control and modulation of charge carrier flow. In a typical FET configuration, such as a metal-oxide-semiconductor field-effect transistor (MOSFET), the device comprises three primary regions: the source, the drain, and the entrance, separated by an insulating oxide layer (usually silicon dioxide, SiO<sub>2</sub>). When a voltage potential is applied to the entrance terminal, it induces an electric field across the oxide dielectric, modulating the energy band profile of the underlying semiconductor channel.

This field effect produces the potential at the semiconductor-insulator interface, enabling control over the charge carriers' conduction channel between the source and drain. The insulating oxide domain acts as a tunneling allowing the electric field to penetrate the semiconductor. This electrostatic entrance mechanism results in an exponential modulation of the channel conductivity, facilitating dynamic switching and

amplification operations. In the realm of information storage systems, particularly non-volatile memory architectures, a dedicated function is essential for reliable data retention and retrieval. But it may have the potential barrier in the system like flash memory, the controlled trapping and retention of charge within the entrance dielectric and within charge trapping will have the potential barrier of using over charge to preventing the electron to escape, in addition, with the barrier properties of charge outflow will limiting the electron (data) capture capability.

To tackle the above situation, this research introduces an innovative partial thin-wall layer methodology designed to sustain and amplify electronic momentum by establishing highly efficient charge transport pathways. The approach enhances charge carrier mobility and supports integrated self-operating functionalities. It facilitates the capture of electrons within silicon-based microcapsules at reduced applied pressure and voltage thresholds. By engineering ultra-thin, highly conductive silicon wall layers, the strategy minimizes electrical resistance, thereby promoting rapid and low-loss electron flow. This optimization optimizes the device's electronic performance, reliability, and energy efficiency while enabling autonomous operational capabilities.

Precise control over the silicon capsule architecture allows electron capture at significantly lower electric fields, reducing activation energy barriers and operational voltages. The technique leverages principles from condensed matter physics including quantum confinement and charge transport dynamics and advanced semiconductor engineering to improve device scalability, robustness, and efficiency within integrated circuit systems.

This innovative partial thin-wall layer (PTWL) aims to sustain momentum by creating efficient electron pathways, enhancing their capabilities, and enabling self-operating functions. It allows electrons to be captured into silicon capsules with lower pressure voltages. The strategy optimizes charge carrier transport through highly conductive, low-resistance pathways (using a Partial thin silicon wall layer) that support rapid electron flow. This improves overall electronic performance and supports autonomous functions. By precisely engineering silicon capsules, the method achieves electron capture at lower electric fields, reducing operational voltage and increasing energy efficiency. It combines principles from condensed matter physics and semiconductor engineering to boost device efficiency.

This segment's innovation approach (partial thin-wall layer) can enhance electron capabilities, demonstrating resilience and flexibility amid changing electron landscapes that make using less voltage can easily catch up with the silicon capacitors, which makes the flash memory can easily capture inside the silicon capsules.

This segment approach has the potential to enhance electron technological capabilities by adopting our (this research paper) advanced innovations, thereby demonstrating resilience and adaptive flexibility within dynamically evolving electronic environments. Such improvements can be achieved through the integration of cutting-edge thin partial wall design, with road path less resistance (silicon wall).

#### Suggestion

This research proposes an innovative partial thin wall layer (PTWL) method to create a device known as a thin-layer transistor that can be integrated into chips. The main idea is that a thin wall can offer less resistance, making it easier for electrons to enter the silicon cap. The process works like a bidirectional diode, consuming less power and increasing efficiency, which can enhance overall device performance.

This innovative thin-wall layer strategy design aims to sustain momentum by establishing efficient pathways for electron flow, enhancing their capabilities, and enabling self-driven functionalities. That is to use less pressure voltage to easily capture the electron into the silicon capsules. This advanced thin-wall layer strategy is designed to optimize charge carrier transport by establishing highly conductive, low-resistance pathways (thin silicon part-wall layer design) that facilitate rapid electron flow, thereby enhancing the overall electronic performance and enabling autonomous functional mechanisms.

The approach leverages precision engineering of silicon capsules to achieve electron capture with reduced applied electric field intensities, thus lowering the operational voltage requirements and improving energy efficiency. This method integrates principles of condensed matter physics and semiconductor device engineering to improve device reliability and efficiency.

**Figure 1.** Partial thin wall layer approach (PTWL) (Author's view).

This segment's innovative approach, known as the partial thin-wall layer (PTWL), aims to enhance electron mobility and device resilience within advanced semiconductor memory architectures. By optimizing the electrode-electrolyte interface and leveraging quantum confinement effects, this methodology can improve the electron injection efficiency and reduce voltage requirements, thus enabling flash memory devices to operate effectively at lower voltages. Such advancements facilitate improved scalability and reliability, allowing the memory cells to maintain performance consistency amid evolving electron landscapes characterized by increased electron density and mobility. Consequently, the integration of PTWL techniques in silicon-based capacitors can lead to enhanced charge storage capacity and faster switching speeds, aligning with industry standards for high-performance, low-power non-volatile memory solutions.

This innovation segment thin wall layer approach (PTWL) can enhance electronic technology capabilities by implementing advanced resilience and adaptability in rapidly evolving electronic environments. These improvements are possible through integrating innovative thin partial wall designs with lower resistance pathways, such as silicon wall.

#### Conclusion

In conclusion, this paper introduced an innovative partial thin wall layer (PTWL) method. This segmentation technique–(partial thin wall layers) aims to advance electronic technology by increasing resilience and adaptability in rapidly evolving electronic settings. These exciting advancements in innovative thin partial wall designs with low-resistance pathways like silicon walls could lead to more powerful and versatile memory chips in the future. Overall, this research aspires to benefit both the industry and humanity.

#### **Declarations**

**Acknowledgments:** The author would like to acknowledge the independent nature of this research, which was conducted without institutional or external support.

**Author Contribution:** The author confirms sole responsibility for the following: study conception and design, data collection, analysis and interpretation of results, and manuscript preparation.

**Conflict of Interest:** The author declares no conflict of interest.

**Consent to Publish:** The author agrees to publish the paper in International Journal of Recent Innovations in Academic Research.

**Data Availability Statement:** All relevant data are included in the manuscript.

Funding: This research received no external funding.

**Institutional Review Board Statement:** Not applicable.

**Informed Consent Statement:** Not applicable.

**Research Content:** The research content of the manuscript is original and has not been published elsewhere.

## References

1. Memory Coalition of Excellence. 2021. Recommendations for the national semiconductor technology center. Electronic Pro Tech Publish Hub.

| 2.  | Young, C. 2020. IoT devices in the public health sector. Cybersecurity Undergraduate Research. https://digitalcommons.odu.edu/covacci-undergraduateresearch/2020spring/projects/6/                                                                                     | 6.  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     |                                                                                                                                                                                                                                                                        |     |

|     | ation: Lie Chun Pong. 2025. Innovative Chips Design: Partial Thin Wall Layer Approach (PTWL                                                                                                                                                                            | ı). |

| Co  | ernational Journal of Recent Innovations in Academic Research, 9(3): 203-206.<br><b>pyright:</b> ©2025 Lie Chun Pong. This is an open-access article distributed under the terms of the Creativ                                                                        |     |

| Con | mmons Attribution License ( <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a> ), which permits unrestricted, distribution, and reproduction in any medium, provided the original author and source are credited. | ed  |