# International Journal of Recent Innovations in Academic Research

This work is licensed under a Creative Commons Attribution 4.0 International License [CC BY 4.0]

E-ISSN: 2635-3040; P-ISSN: 2659-1561 Homepage: https://www.ijriar.com/ Volume-9, Issue-3, July-September-2025: 215-217

# **Research Article**

# An Innovative Method: Total Thin Wall Layer (TTWL) Approach in Producing Memory Chips

# **Lie Chun Pong**

MEd, CUHK (Chinese University of Hong Kong), MSc, HKUST (Hong Kong University of Science and Technology)

Email: vincentcplie@yahoo.com.hk

**Received:** July 31, 2025 **Accepted:** August 20, 2025 **Published:** August 26, 2025

## **Abstract**

Traditional memory chip design encountered major challenges caused by outflow currents in diodes after repeated cycles, which hindered the reliable closing of the memory cell access. To address this, recent efforts have focused on re-engineering existing methods to improve electrical isolation and stability. In our research study, we introduce an innovative method called Total Thin Wall Layer (TTWL) approach. This innovative method can effectively smooth out the previously problematic access pathways. A thin-wall layer with thin-wall silicon entrance can make less resistance in accordance with the electron flow, which means it is more easier to allow the electron to flow into the silicon capsules. The aim is to balance the conventional memory particle applications with integration that uses less energy consumption, which can boost overall robustness and performance.

Keywords: Memory Chips, Total Thin Wall Layer, Silicon Capsules.

#### Introduction

In this research paper, we present a novel approach to device architecture, specifically employing a Total-Thin-Wall Layer (TTWL) configuration. This design is implemented within a memory domain integrated circuit (IC) and offers a promising solution associated with conventional memory device structures. The proposed TTWL-based device architecture enhances structural robustness and thermal management while potentially improving data retention and switching speed. This innovative configuration addresses the limitations of traditional thick-wall layered devices by minimizing material usage and optimizing layer interfaces, thus advancing the performance and reliability of next-generation non-volatile memory systems.

# **Discussion**

Traditional metal-oxide-semiconductor field-effect transistors (MOSFETs) are built with a simple three-layer structure. They include heavily doped source and drain areas, a silicon dioxide dielectric layer, and a conductive entryway electrode. When a voltage is applied to the entryway, it creates an electric field across the dielectric, which alters the potential barrier and enables charge carriers to be injected from the source into the channel [1] in a controlled manner. This electrostatic control manages the channel's conductivity, controlling current flow between drain and source. The wall layer functions as a tunneling-barrier, limiting charge movement and making it possible to store data non-volatilely, as in a memory cargo. This fundamental principle is the backbone of many advanced digital logic and memory devices, where precise charge control is key. However, there's a major problem that the industry need to overcome, like the current leakage issue [1, 2].

In the traditional approach, the problem was that the diode had a very high leakage current, making it difficult for the electrons to flow into the capsules as they should. That means, the issue stems from the diode exhibiting a significantly elevated leakage current, which hampers the efficient injection and collection of charge carriers-specifically electrons-into the encapsulated structures. This excessive leakage current impairs the diode's rectification and switching capabilities, thereby reducing overall device performance [1, 2]. To address this limitation, we proposed a Total Thin Wall Layer (TTWL) design, embedded in silicon to create a thin wall layer entrance transistor. This design provides a substantial increase in speed and ensures excellent process compatibility. Additionally, it greatly reduces power consumption.

An entrance structure is integrated into the dielectric wall to create a Total Thin Wall Layer (TTWL) entrance system, common in advanced MOSFETs. This design increases switching speed threefold by reducing the thickness, which can enhance capacitance and charge carrier mobility. It also works well with standard CMOS fabrication processes, allowing for easy inclusion in current semiconductor manufacturing. Additionally, this method significantly reduces static and dynamic power consumption by lowering leakage currents and improving electrostatic control, which is vital for low-power, high-performance integrated circuits.

Additionally, implementing a Total Thin Wall Layer Transistor (TTWLT) architecture simplifies complex circuits by replacing many transistors with a more integrated and efficient design, significantly reducing the silicon area needed and improving spatial efficiency. When the silicon wall and entrance wall thickness decrease, electrons are more easily captured inside the silicon capsules. For instance, a CPU-connected on-chip dynamic cache, which typically requires numerous transistors for control and storage, can be reduced to about 15-25% of its original size. This miniaturization benefits from TTWLTs, offering better control entrance coupling, fewer parasitic effects, and improved scalability in advanced CMOS nodes. This architectural change not only boosts packing density but also lessens parasitic capacitance and enhances switching speed, ultimately improving system performance and energy efficiency.

Also, the development and implementation of a more advanced device architecture such as utilizing a diode with optimize electron transport, minimize leakage pathways, and enhance operational reliability. Such improvements are critical in ensuring device efficiency aligns with the stringent requirements of modern electronic and optoelectronic applications, adhering to IEEE standards and other relevant physics-based design principles.

# **Suggestion**

A Total Thin Wall Layer (TTWL) design, embedded in the silicon to form a thin wall layer entrance transistor is our innovative suggestion. This design offers a substantial increase in speed and ensures excellent process compatibility. Moreover, it significantly reduces power consumption.

Our novel methodology employs a device architecture predicated on a total-thin-wall layer configuration within memory domain integrated circuits. This innovative structural design addresses the longstanding solution associated with traditional memory technologies by enhancing scalability, thermal stability, and endurance. Such integration leverages advanced material science principles and condensed matter physics to optimize electron mobility, signal integrity, and device miniaturization, thus providing a superior solution aligned with the rigorous standards of IEEE and contemporary physics research.

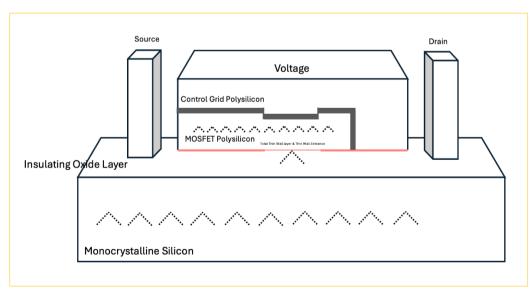

**Figure 1.** Innovative approach [total thin wall layer (TTWL) approach in producing memory chips] (Author's view).

This advanced technique involves the strategic modification of access pathways within the semiconductor structure to mitigate previously encountered barriers that impeded efficient electron transport. A nanoscale, silicon-based total thin-wall layer functions as an entrance interface, significantly reducing contact

resistance and facilitating more efficient charge carrier injection into the silicon capsules. The primary objective is to optimize the trade-off between conventional memory particle applications, such as phase-change or resistive RAM, and power alternatives, thereby improving device robustness, energy efficiency, and overall operational reliability. This methodology leverages principles from condensed matter physics and electronic materials engineering to enhance charge mobility and device endurance.

#### Conclusion

In conclusion, this research paper introduces a new device architecture using a Total-Thin-Wall Layer (TTWL) design. Integrated into a memory domain IC, this structure provides a promising alternative to traditional memory devices. The TTWL-based design improves durability and thermal regulation, while also potentially boosting data retention and switching speed. It tackles the drawbacks of conventional thick-wall layered devices by reducing material use and optimizing layer interfaces, thereby enhancing the performance and reliability in future non-volatile memory systems.

#### **Declarations**

**Acknowledgments:** The author would like to acknowledge the independent nature of this research, which was conducted without institutional or external support.

**Author Contribution:** The author confirms sole responsibility for the following: study conception and design, data collection, analysis and interpretation of results, and manuscript preparation.

**Conflict of Interest:** The author declares no conflict of interest.

**Consent to Publish:** The author agrees to publish the paper in International Journal of Recent Innovations in Academic Research.

**Data Availability Statement:** All relevant data are included in the manuscript.

**Funding:** This research received no external funding. **Institutional Review Board Statement:** Not applicable.

**Informed Consent Statement:** Not applicable.

**Research Content:** The research content of the manuscript is original and has not been published elsewhere.

# References

- 1. Hosomi, S., Honda, S., Inada, M., Sato, S., Tani, H., et al. 2025. Signature of Dirac fermion injection from hole-doped graphene into two-dimensional semiconductors. Science and Technology Reports of Kansai University, 67: 13-19.

- 2. Zhao, W., Melliar-Smith, P.M. and Moser, L.E. 2010. Fault tolerance middleware for cloud computing. In: Proceedings of the 2010 IEEE 3<sup>rd</sup> international conference on cloud computing (pp. 67-74). IEEE.

**Citation:** Lie Chun Pong. 2025. An Innovative Method: Total Thin Wall Layer (TTWL) Approach in Producing Memory Chips. International Journal of Recent Innovations in Academic Research, 9(3): 215-217.

**Copyright:** ©2025 Lie Chun Pong. This is an open-access article distributed under the terms of the Creative Commons Attribution License (<a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>), which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.