# International Journal of Recent Innovations in Academic Research

This work is licensed under a Creative Commons Attribution 4.0 International License [CC BY 4.0]

E-ISSN: 2635-3040; P-ISSN: 2659-1561 Homepage: https://www.ijriar.com/ Volume-9, Issue-3, July-September-2025: 259-262

#### **Research Article**

# An Innovative Method: Flat Curve Thin Len Layer Wall (FCTLLW) Approach in Producing Flash Memory Chips

### **Lie Chun Pong**

MEd, CUHK (Chinese University of Hong Kong), MSc, HKUST (Hong Kong University of Science and Technology)

Email: vincentcplie@yahoo.com.hk

**Received:** August 07, 2025 **Accepted:** August 26, 2025 **Published:** September 01, 2025

#### **Abstract**

Traditional memory chip design faced significant challenges because outflow currents in diodes after repeated cycles hindered the reliable closing of the memory cell access. Therefore, new methodologies must be developed to re-engineer existing approaches to improve electrical isolation and stability, effectively smoothing out the previously problematic access pathways, is a must. In this research paper, the goal is to balance the needs of conventional memory applications with advance techniques that enhance overall robustness and performance by introducing a new innovative concept: Flat Curve Thin Len Layer Wall (FCTLLW) approach in producing memory chips. We hope to boost the capabilities of flash memory storage and set a new industry standard.

**Keywords:** Flat Curve Thin Len Layer Wall, Flash Memory Chips, Challenges.

#### Introduction

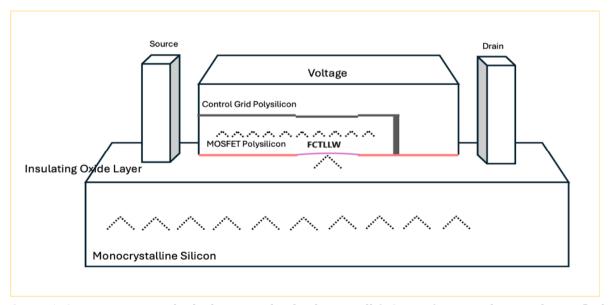

Traditional transistors consist of three layers that work together to store information. When a voltage is applied to the top layer, charges from the bottom layer can pass through a barrier formed by an insulating oxide layer, reaching the middle silicon layer. This design enables effective control of charge movement, facilitating reliable data storage. But the problem was that the diode had a very high leakage current after multiple cycles, preventing the entrance from closing properly [1].

So, what method and solution can address the issue mentioned above? The answer typically depends on the material size and the process used to form the insulating oxide layer. This forms the basis of how the entrance on the wall has developed. To resolve the gymnasium process, the new silicon capsule must function like a bidirectional diode, dealing with charging and electron leakage problems.

#### Discussion

To open this well-intentioned but firmly closed traditional method of entrance, which meets the criteria suitable for traditional use, along with the advancement, an innovative concept device known as a flat curve thin-layer lens transistor has emerged with the advancement of conceptual technology.

As previously mentioned, traditional memory chip design faced major challenges due to outflow currents in diodes after multiple cycles, which hindered the reliable closing of the memory cell access. Although previously many efforts were made to re-engineer existing techniques to improve electrical isolation and stability, these efforts did not resolve the problem [2]. In other words, using a better device could be the solution. Our innovative approach involves a device format based on a Flat Curve Thin Len Layer Wall (FCTLLW) approach used in a memory domain chip, which is the only way to solve the traditional problem. Our method can effectively smooth out the previously problematic access pathways. This innovative concept aims to balance the needs of conventional memory applications with integration techniques that enhance overall robustness and performance.

## **Discussion and Insights**

The innovative concept is actually quite logical. Imagine you are sitting on a high-speed train. The seats are originally closed and there is no extra space on both sides. Now, if we can thin out the originally closed space

on both sides of the seats to create a certain amount of space on both sides, we can use the extra space to place things. For example, wallets, mobile phones, etc., so our (new concept idea) model structural (pocket thinness) is the most ideal for constructing chip design new coatings.

Firstly, the extra space can store more electrons (memory particles); secondly, electrons (memory particles) can be stored with less voltage, which really kills two birds with one stone. This innovative structure is operational, practical, and feasible in actual applications.

The concave surface can more easily absorb more charged memory particles. In the application of physics, the flat curved surface, under the action of light, not only make the particles more focused and aggregated, also, making it easier for particle pairs and electrons to gather, also, the flat curved surface's thin design can also make (memory particles) gather more. In addition, the smooth reflection of the same section in the curved surface can use less energy and make it easier to store (memory particles) in the capsule. That is, less energy and less voltage can be used to store electrons (memory particles) inside. It really solves two problems at once stone, so that a flat thin concave lens on one side can have two cross-sections, one on the concave side and the other on the convex side, and the two functions of one input and one reflection can be achieved at the same time. This can boost up the saving in flash memory.

Some may wonder whether internal reflective phenomena within the encapsulating microstructure could cause localized electromagnetic field enhancements, leading to concentrated energy deposition and subsequent thermal robustness effects. However, these concerns are effectively addressed by the innovative microstructure design proposed in this study. The encapsulation architecture uses a tailored capture mechanism that prevents energy concentration. This approach applies principles from electromagnetic theory and thermal management to ensure uniform energy distribution and avoid hotspot formation. By incorporating these design strategies, the system maintains thermal stability, thus preventing catastrophic failure modes and improving device reliability in accordance with IEEE standards for electromagnetic compatibility.

The primary objective of this research is to min the power consumption so that less voltage can operate voltage parameters while significantly enhancing the data storage density of flash memory devices. In this context, the implementation of efficient planar micro-curved reflective structures within silicon-based encapsulation chambers can facilitate more effective manipulation of electromagnetic reflection and internal optical pathways, thereby smoothing the memory's operational efficacy while minimizing energy expenditure. The corporation of smooth, micro-curved surfaces not only enhances the physical robustness of the encapsulation, but also contributes superior mechanical characteristics. Consequently, this innovative structural approach demonstrates feasibility from theoretical modeling, fabrication processes, and practical application perspectives, ensuring reliable operation under normal and demanding conditions.

Additionally, this innovative method can leverage storage capacity, especially in the flash memory domain, which in turn minimizes energy use and saves more (memory particles). But some individuals may curiosity that electrons may temporarily slide out their atomic orbits in the flat thin concave lens structure when subjected to focused electromagnetic fields. Contrary to this misconception, electrons are fundamentally subatomic particles possessing intrinsic magnetic moments, which confer upon them specific electromagnetic interactions. Therefore, a flat thin concave design can smooth the process of capturing the (memory particle) inside the capsules. Instead of sliding out.

Despite exhibiting wave-like properties as described by quantum mechanics such as delocalization and interference-electrons are primarily influenced by Coulombic forces and magnetic interactions due to their charge and magnetic dipole moment. These interactions facilitate their attraction to nuclei within atomic structures. Therefore, the electrons will not 'slip out' of orbits under flat thin concave lens design. Also, in the convex side, the reflective part can smooth the flash memory to formation. In the quantum and electromagnetic principles governing their behavior, which are predominantly characterized by attractive Coulombic potentials and magnetic coupling rather than mere pure impact interaction inside the silicon capsule.

This innovative design (FCTLLW) incorporates the attraction of electron-like particles, often conceptualized as 'memory particles,' utilizing electrostatic or electromagnetic forces. It's important to clarify that surface smoothness, in this context, does not necessarily equate to a mirror-like; rather, it pertains to the optimized surface topology to facilitate particle flow. Accurately, it will draw electron (memory) particles, and

smoothness. The flat curve thin len design does not alter the chip's original mechanism. It simply makes the wall thinner to increase memory capacity. The principle of the curved surface is to make it easier and smoother for (memory particles) position to flow toward the curved surface. This design complies with the laws of physics and aligns with electron-like particles operations.

#### **Suggestion**

The flat-curve-thin-lens-wall-layer configuration can be effectively engineered and integrated into a memristive or electronic flash memory chip architecture. This transformation leverages advanced nanofabrication techniques to realize a compact, scalable, and high-speed memory node, utilizing the unique optical and plasmonic properties of the device structure. Such a device can be modeled and analyzed using rigorous electromagnetic simulations based on Maxwell's equations and quantum electrodynamics, ensuring compliance with IEEE standards for integrated photonics and optoelectronic components.

This innovative advanced thin, curved-layer lens architecture facilitates enhanced electron confinement through a more efficient clustered capture mechanism. The thin concave lens layer make the electron easier to flow in the capture focus pt, the opposing surface of the lens incorporates a convex protrusion designed to optimize particle collection efficiency within the device. Its refractive index is engineered to minimize electromagnetic energy dissipation, thereby reducing overall energy consumption. The convex protrusion also serves to streamline the insertion process of the underlying flash memory module, ensuring greater operational stability and secure engagement. This innovative design reduces energy expenditure while expanding the optical pathway channel. Consequently, it potentially enhances the flash memory system's ability at the focal region, thereby supporting improved memory particle localization, which in turn improve data retention capabilities in memory chip storage technologies.

**Figure 1.** An innovative method: Flat curve thin len layer wall (FCTLLW) approach in producing flash memory chips.

A novel device termed a 'Flat Curve Length Thin-Layer Transistor' (FCL-TLT) has been designed by our research, representing an advancement in the field of electronic and optoelectronic components. This device operates affiliated to a bidirectional diode with enhanced charge transport efficiency, leveraging the unique properties of thin-layer semiconductor physics. Comprehensive simulations, utilizing finite element analysis and quantum transport models, have been conducted to rigorously assess its operational feasibility and to optimize its structural parameters for maximum performance. The underlying mechanisms involve intricate electrostatic and quantum effects, potentially opening new avenues for high-efficiency, flexible, and miniaturized electronic circuits.

With the implementation of our novel curve length thin-layer methodology, we posit that this innovative approach has the potential to provide a more comprehensive and nuanced perspective on prevailing industry practices and the design paradigms of flash memory chips. This method represents a notable progression in modeling thin-layer structures, which could improve performance and reliability in flash memory devices.

#### Conclusion

Machine and technology advancements are essential for maintaining competitiveness in high-precision physics applications and computer chips industrial processes. This development improves the sector's capacity to adapt to fast technological shifts and ensures it meets the rigorous standards of IEEE protocols and scientific precision typical in contemporary physics research. This research paper presents an innovative approach fulfills the specified requirement and aligns seamlessly with IEEE and industry standards. Our innovative flat curve thin len layer wall (FCTLLW) approach in producing flash memory chips aims to provide a fresh perspective on industry practices and the design of advanced flash chips.

#### **Declarations**

**Acknowledgments:** The author would like to acknowledge the independent nature of this research, which was conducted without institutional or external support.

**Author Contribution:** The author confirms sole responsibility for the following: study conception and design, data collection, analysis and interpretation of results, and manuscript preparation.

**Conflict of Interest:** The author declares no conflict of interest.

**Consent to Publish:** The author agrees to publish the paper in International Journal of Recent Innovations in Academic Research.

**Data Availability Statement:** All relevant data are included in the manuscript.

Funding: This research received no external funding.

**Institutional Review Board Statement:** Not applicable.

**Informed Consent Statement:** Not applicable.

**Research Content:** The research content of the manuscript is original and has not been published elsewhere.

#### References

- 1. Li, B. and Hou, Y.T. 2016. The new automated IEEE INFOCOM review assignment system. IEEE Network, 30(5): 18-24.

- 2. Goswami, D. and Chakraborty, A. 2015. Sensitizing engineers: A brief study of the role of ethics in engineering education. In: 2015 5<sup>th</sup> Nirma University international conference on engineering (NUiCONE) (pp. 1-4). IEEE.

**Citation:** Lie Chun Pong. 2025. An Innovative Method: Flat Curve Thin Len Layer Wall (FCTLLW) Approach in Producing Flash Memory Chips. International Journal of Recent Innovations in Academic Research, 9(3): 259-262.

**Copyright:** ©2025 Lie Chun Pong. This is an open-access article distributed under the terms of the Creative Commons Attribution License (<a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>), which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.